New progress in 3-D memory IC design of SIMIT

Date:13-09-2017 | 【Print】 【close】

Recently, Phase Change Random Access Memory (PCRAM) research group of the Shanghai Institute of Micro-system and Information Technology (SIMIT), Chinese Academy of Sciences (CAS) made an important progress in 3-D memory integrated circuit (IC) design. The research work has been published electronically on IEEE Transactions on Circuits and Systems II: Express Briefs [vol. PP, no. 99, 2017], which is an important journal in IC design, with the title of “A Single-Reference Parasitic-Matching Sensing Circuit for 3-D Cross Point PCM”. This article is the first article on 3-D PCRAM IC design.

Non-volatile phase-change random-access memory (PCRAM) is regarded as a leading candidate for next-generation electronic memory hierarchy. It utilizes the pronounced electrical resistance difference between the amorphous and crystalline states of chalcogenide phase change materials (PCMs) to encode digital information.

3D ICs can be divided into 3D Stacked ICs and monolithic 3D ICs, which use fab processes to realize 3D interconnects at the local levels of the on-chip wiring hierarchy as set forth by the ITRS, this results in direct vertical interconnects between device layers. Among the monolithic 3D ICs, 3-D cross point phase change memory (PCM) is considered to be a leading 3-D technology for emerging nonvolatile memories.

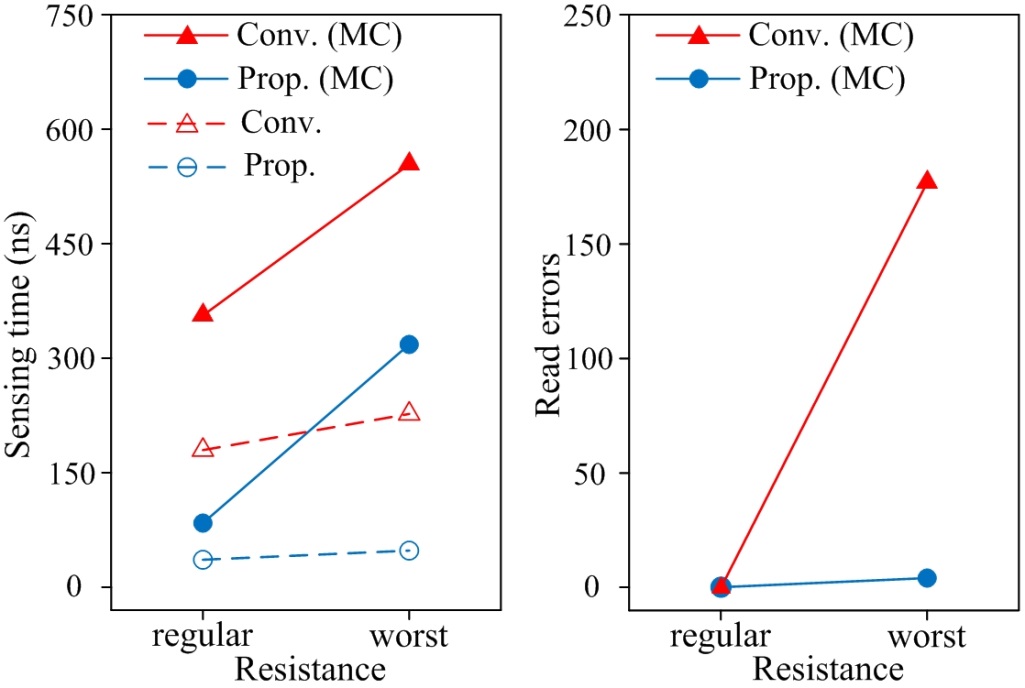

Up to now, studies of 3-D cross point memory are mainly focused on the devices and materials. However, it has been rarely reported the detailed analysis of parasitic parameters of the read operation and the sensing circuit that relates to the specific characteristics of 3-D emerging NVMs. Besides planar parasitic elements, vertical parasitic elements will also delay the read operation in 3D PCM. Dr. Yu Lei and others of SIMIT conclude the five factors that affect the read operation in 3-D cross point PCM for the first time. They then proposed a single-reference parasitic-matching sensing circuit to speed up the read operation. Simulated in a 40nm CMOS process, the sensing time of 64Mbit 3-D cross point PCM is 39.67ns compared to the conventional 185.3ns. Monte Carlo simulations show an 84.5ns worst sensing time compared to the conventional 364.5ns.

The proposed sensing circuit can be utilized in different 3-D emerging NVMs and speed up the sensing speed for memories with different capacities.

This paper concludes the five factors that affect the read operation of 3-D cross point emerging NVMs and their relationships to the array for the first time, purposes the first sensing circuit whose design is related to the specific characteristics of 3-D emerging NVMs and also be the first paper on 3-D PCRAM IC design.

Dr. Yu Lei is the first author of the article. Professor Houpeng Chen is the corresponding author. The research work is led by Professor Zhitang Song. The manuscript was submitted in Dec. 2016. This work was supported in part by the “Strategic Priority Research Program” of the Chinese Academy of Sciences, by the National Integrate Circuit Research Program of China, by the National Natural Science Foundation of China, and by the Science and Technology Council of Shanghai.

Paper link: http://ieeexplore.ieee.org/document/7987059/

DOI: 10.1109/TCSII.2017.2729665

Figure 1 The array architecture of 3-D cross point PCM

Figure 2 The purposed reference circuit

Figure 3 Read performance comparisons between the proposed circuit and the conventional circuit